Startups, students key to boost DIR-V ecosystem, develop indigenous chips: MoS IT

In order to make India a leading chip design and manufacturing nation, startups, students and entrepreneurs will play a crucial role in developing Digital India RISC-V (DIR-V)-based chips and systems, further catalysing the semiconductor ecosystem while adopting open-source technologies, Minister of State for Electronics and IT, Rajeev Chandrasekhar, said on Friday.

image for illustrative purpose

New Delhi, Nov 17 : In order to make India a leading chip design and manufacturing nation, startups, students and entrepreneurs will play a crucial role in developing Digital India RISC-V (DIR-V)-based chips and systems, further catalysing the semiconductor ecosystem while adopting open-source technologies, Minister of State for Electronics and IT, Rajeev Chandrasekhar, said on Friday.

The minister flagged off the a nationwide roadshow on DIR-V programme, jointly organised by C-DAC, IEEE India Council and Ministry of Electronics & IT (MeitY), with participation from global leaders in the RISC-V design area.

SHAKTI processors by IIT Madras and VEGA processors by C-DAC are anchoring the DIR-V ecosystem, enabling collaboration with startups and entrepreneurs.

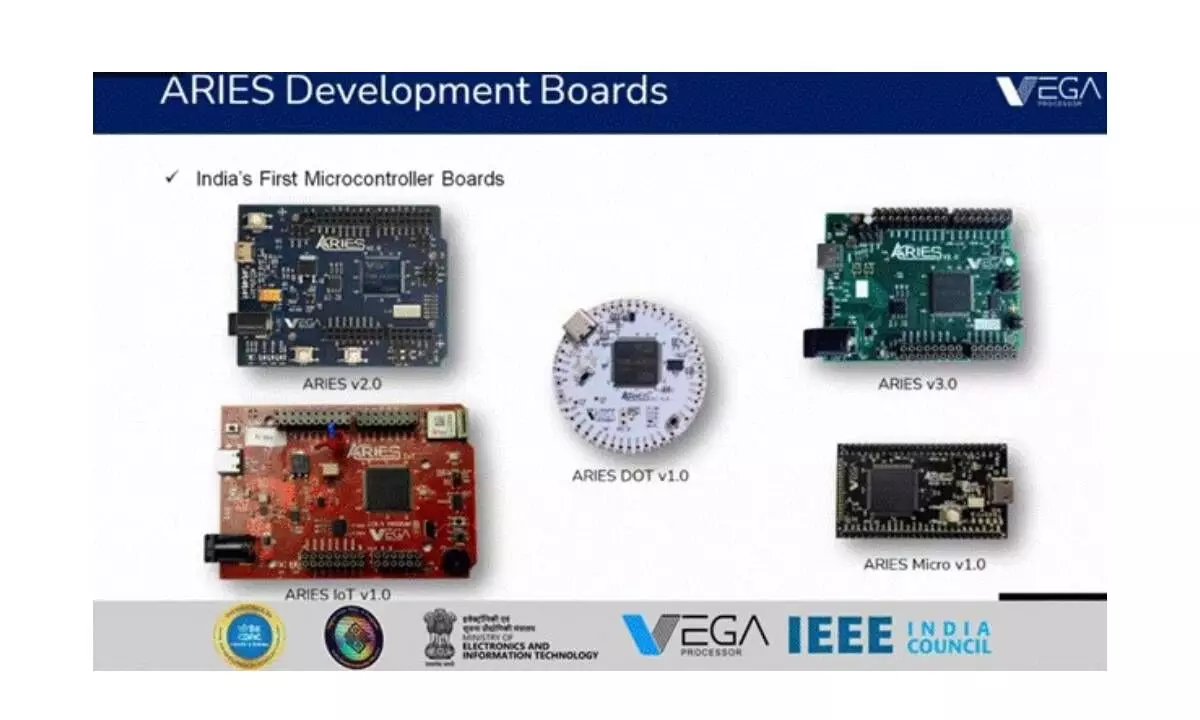

C-DAC has also created a series of ARIES development boards based on VEGA chip. These development kits are fully indigenous and India-made products targeted for learning, embedded system design and IoT applications. The boards come with easy-to-use hardware and software.

According to Chandrasekhar, the DIR-V programme is playing a pivotal role in realising the vision laid by Prime Minister Naremdra Modi to create and adopt open-source technologies.

“Our prime focus is to enable the growth of the DIR-V ecosystem, aiming for India to emerge as a leading nation in innovating around the DIR-V family of chips and systems,” he said.

The minister highlighted how the programme will ensure DIR V-based chips and systems are integrated into various digital products we use daily.

“India has also embraced RISC-V in flagship government projects, witnessing growth in startup research and innovation around RISC-V. India hosts several startups working on RISC-V-based designs, which are also part of MeitY’s ‘futureDESIGN’ initiative,” said the minister.

The roadshow aims to provide 1,500 participants with valuable insights into the DIR-V VEGA series of processors and their ecosystem, covering both theoretical and practical aspects, including the use of development boards, SDK, and application development. Hands-on sessions will be conducted using the ARIES development boards, featuring video addresses by prominent global leaders. This event is being concurrently held at 15 academic institutions across the country.